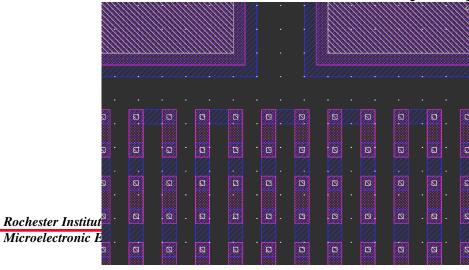

## ROCHESTER INSTITUTE OF TECHNOLOGY MICROELECTRONIC ENGINEERING

# **CMOS** Testing for the Student Run Factory

## Dr. Lynn Fuller

Webpage: <a href="http://people.rit.edu/lffeee">http://people.rit.edu/lffeee</a>

Microelectronic Engineering

Rochester Institute of Technology

82 Lomb Memorial Drive

Rochester, NY 14623-5604

Tel (585) 475-2035

Fax (585) 475-5041

Email: Lynn.Fuller@rit.edu

Department webpage: <a href="http://www.microe.rit.edu">http://www.microe.rit.edu</a>

Rochester Institute of Technology

Microelectronic Engineering

Revised 9-28-2009 cmostest.ppt

### **OUTLINE**

Introduction

Test Structures

Test Equipment

Resistive Tests

Transistors

Integrated Circuits

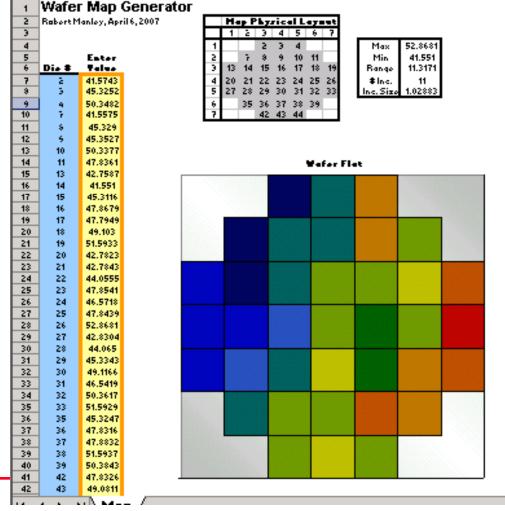

Wafer Mapping

### **INTRODUCTION**

Completed factory wafers are tested as part of the manufacturing process to capture data on processing parameters and transistor characteristics. Some simple integrated circuits are tested to verify functionality of more complex circuits. Uniformity is evaluated by measuring some parameters, such as threshold voltage, over the entire wafer.

These tests are broken into four tasks that can be completed in our normal three hour laboratory time: 1. sheet resistance and contact resistance, 2. transistors, 3. inverters, ring oscillator and op amp, and 4. wafer map of NMOSFET threshold voltage.

More complex digital and analog integrated circuits are tested outside of the factory by those who are interested.

### **INTRODUCTION**

Chip designs always include test structures for the factory in addition to the specific integrated circuit or microsystem being fabricated. The test structures are often located along the edges of the chip and might even be removed after testing during the wafer sawing process. These test structures are available as cells that can be easily added to the integrated circuit or microsystem design. The test setups can be used for all completed chips. Automated probing (rarely done at RIT) may require different setups if the test structures are in different locations on the wafer.

Three other documents provide additional details:

CMOSTestchip2008.pdf - description of latest factory chip CMOSTEST\_Manual.pdf -details for test equipment operation TestResults.pdf - recent factory test results and template for reporting test results

### TEST STRUCTURES

List of factory test structures:

Van Der Pauw's for sheet resistance

CBKR's for contact resistance

NMOS and PMOS transistors of various sizes

Field Oxide NMOS and PMOS transistors

Inverter

Ring Oscillator

Op Amp

Metal serpentine's

Via Chains

Rochester Institute of Technology

Microelectronic Engineering

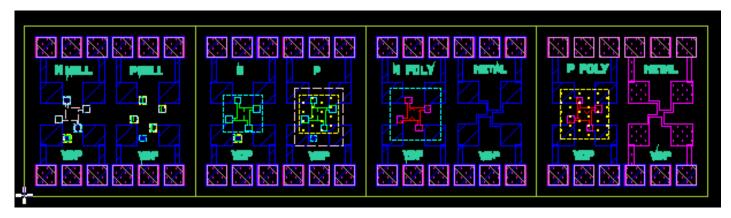

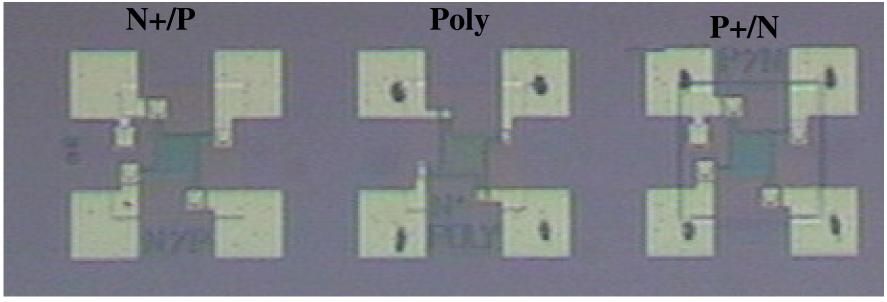

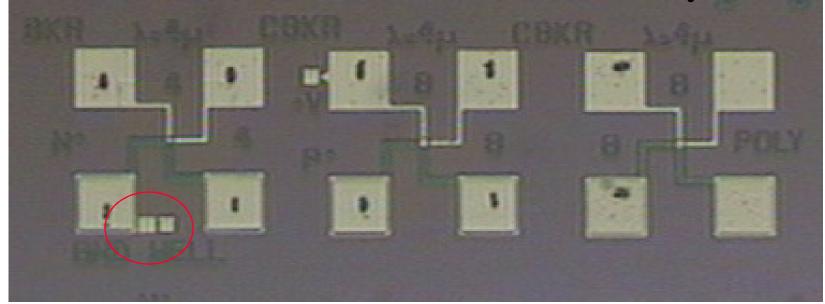

## VAN DER PAUW'S AND CBKR'S

NWELL PWELL N+ P+ N-POLY M1 P-POLY M2

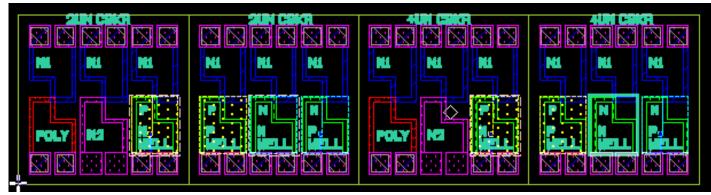

2μm M1toPoly 2μm M1toM2 2μm M1toP+ 2μm M1toP+ 2μm M1toN+ 2μm M1toN+

4μm M1toPoly 4μm M1toM2 4μm M1toP+  $\begin{array}{l} 4\mu m \; M1 to P+ \\ 4\mu m \; M1 to N+ \\ 4\mu m \; M1 to N+ \end{array}$

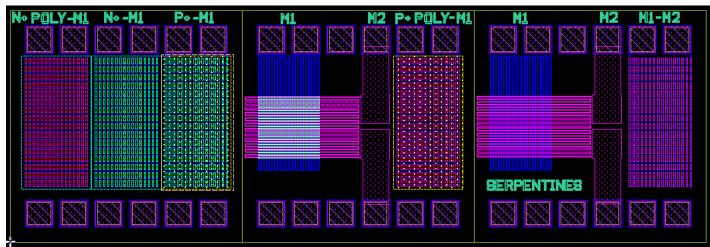

## SERPENTINES, COMBS, AND VIA CHAINS

To evaluate metal1, metal2, CC and Via layer quality.

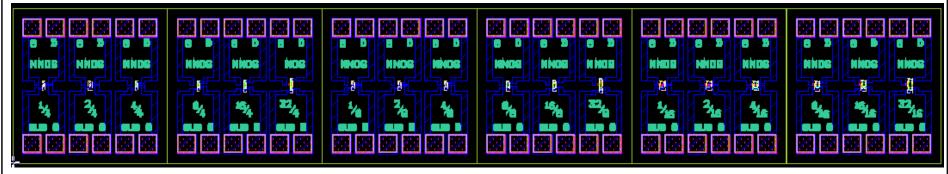

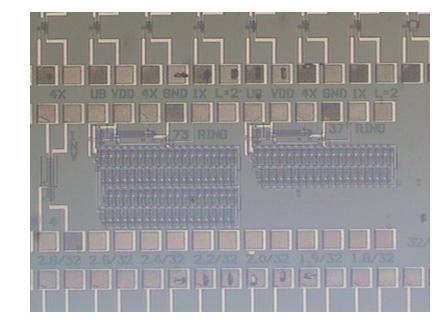

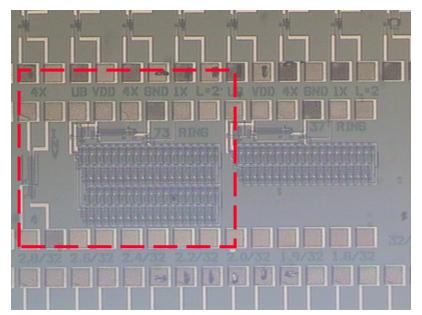

### NMOS AND PMOS TRANSISTORS

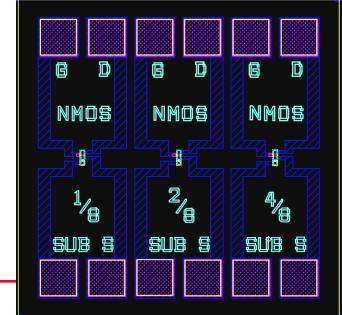

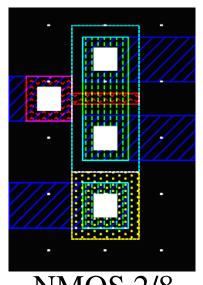

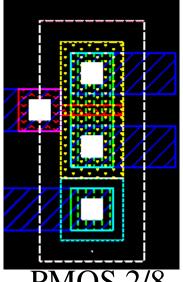

1/8 2/8 4/8 8/8 16/8 32/8 1/32 2/32 4/32 8/32 16/32 32/32 1/4 2/4 4/4 8/4 16/4 32/4

Various L/W Ratios

**NMOS 2/8**

**PMOS 2/8**

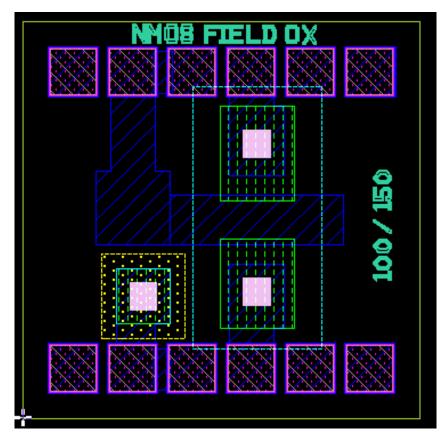

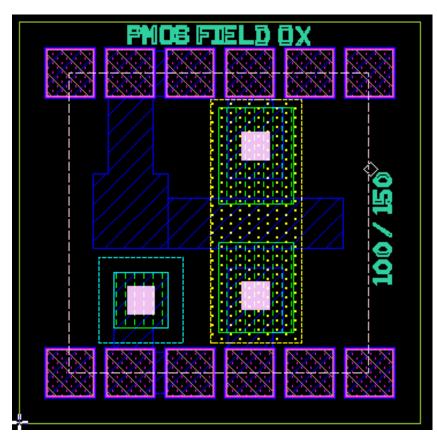

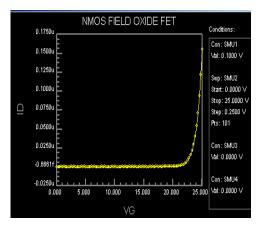

## FIELD OXIDE NMOS AND PMOS FET'S

Rochester Institute of Technology

Microelectronic Engineering

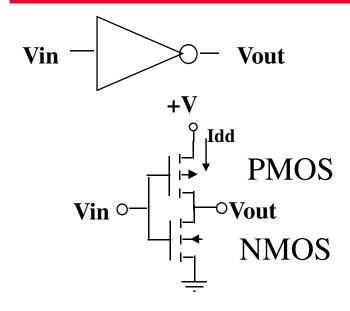

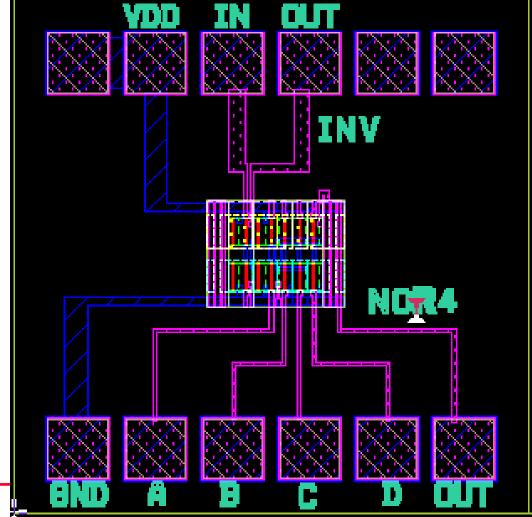

### **CMOS INVERTER**

### **CMOS**

#### **TRUTH TABLE**

| VIN    | VOUT |

|--------|------|

| 0<br>1 | 1 0  |

Rochester Institute of Technology Microelectronic Engineering

$W = 40 \mu m$

$Ldrawn = 2.5 \mu m$

Lpoly =  $1.0\mu m$

Leff =  $0.35 \mu m$

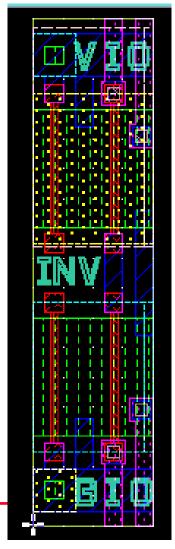

## **INVERTER WITH PADS**

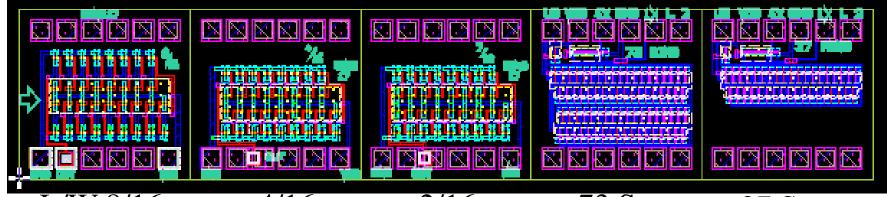

### **RING OSCILLATORS**

17 Stage Un-buffered Output

L/W=2/30 Buffered Output

L/W 8/16

4/16

2/16

73 Stage

37 Stage

Rochester Institute of Technology

Microelectronic Engineering

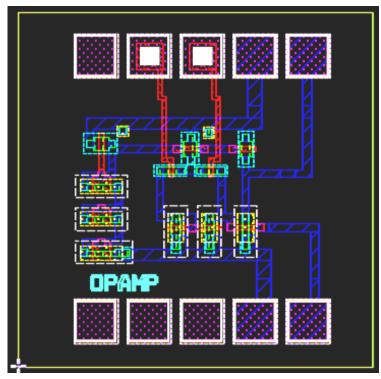

### **OPERATIONAL AMPLIFIERS**

Version 1

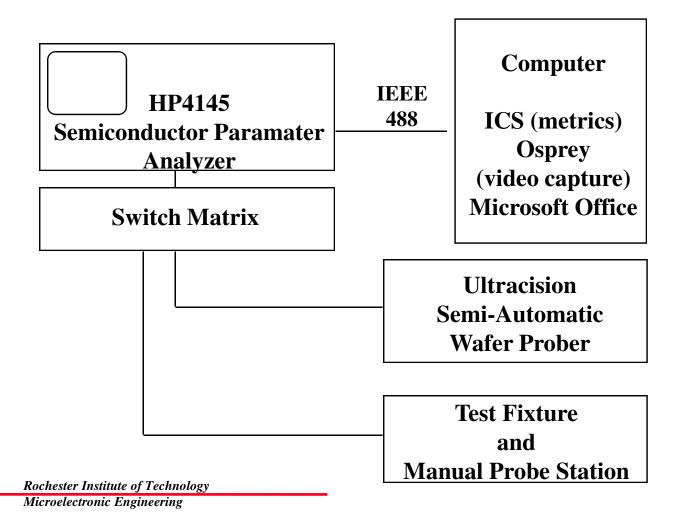

## TEST EQUIPMENT

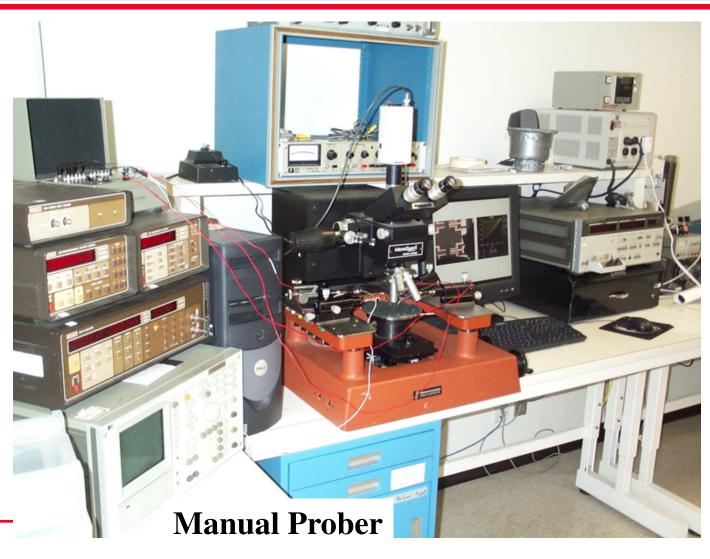

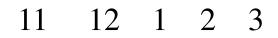

## TEST EQUIPMENT

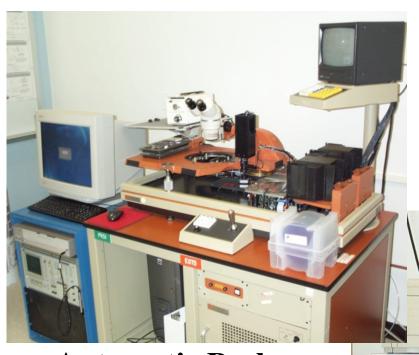

**Semi-Automatic Prober**

## TEST EQUIPMENT

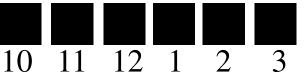

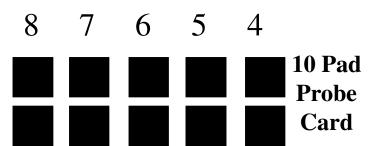

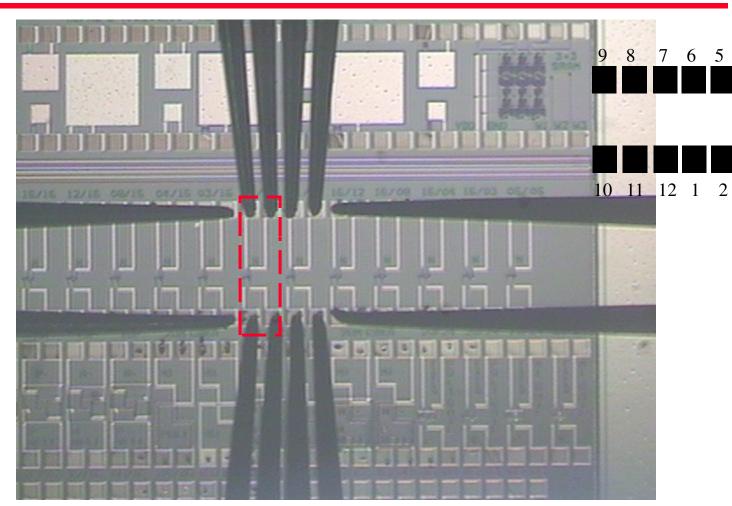

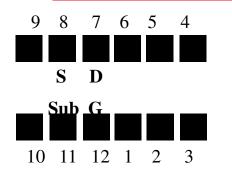

### STANDARD PROBE CARDS & SWITCH MATRIX

Numbers indicate switch matrix column

12 Pad Probe Card

**Probe Card**

### **SWITCH MATRIX**

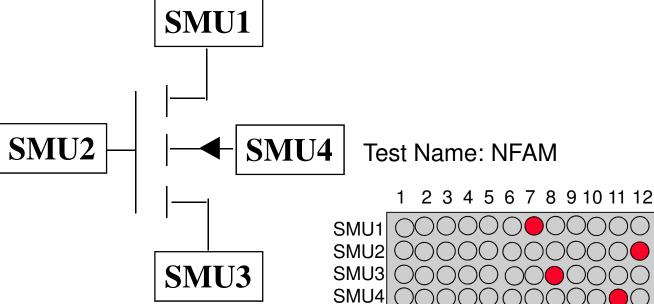

The HP-4145 SMU-1 is connected to row 1, SMU-2 to row 2, SMU-3 to row 3 and SMU-4 to row 4. The probe pins are connected to the columns. The switch matrix indicator above shows SMU1 connected to col. 1 which is the 4<sup>th</sup> pin on the bottom row of the 12 pad probe card (see previous page)

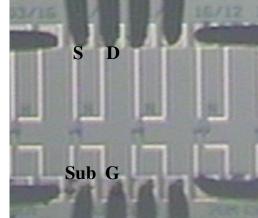

### PROBING A NMOS TRANSISTOR

8 7 S D

Sub G 11 12

Rochester Institute of Technology Microelectronic Engineering

2/16 L/W NMOS FET

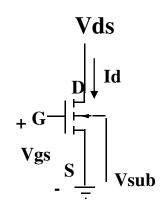

## ICS TEST SET UP for NMOSFET FAMILY OF CURVES

|     | SMU1 | Vds | Sweep 0 - 5 V, 101 steps |

|-----|------|-----|--------------------------|

|     | SMU2 | Vgs | 11 Steps 0 - 5V          |

| ıte | SMU3 | Com | Vs = 0                   |

| Ei  | SMU4 | Com | 0 V                      |

### GENERAL TEST INSTRUCTIONS

Test die in the center of the wafer, then upper left, upper right, lower right, and lower left (about ½ way between center and edge). Extract parameter values from the test results.

Create a PowerPoint document from **test\_results.ppt** master (see example data powerpoint a few pages below) on Dr. Fullers webpage at <a href="http://people.rit.edu/lffeee/labnotes.htm">http://people.rit.edu/lffeee/labnotes.htm</a> (save as) record Lot#, Wafer#, Die location (center, top left,etc), pictures of die, test results graphs, extracted parameters and comments. Email to Dr. Fuller at <a href="Lynn.Fuller@rit.edu">Lynn.Fuller@rit.edu</a>

Test 01 – Van Der Pauw and CBKR. Record Average of five tests

Test 02 – Transistors, test small transistors (L=2μm for SMFL,

L=1µm for Sub-CMOS and Adv-CMOS). Record results in power point document.

Test 03 – Inverters, Ring Oscillator. Record Average of five tests.

Test 04 – NMOS VT wafer map

### GENERAL TEST INSTRUCTIONS

Substrate or Well Connections: Most of the test structures incorporate diffusions. In Resistors, Van der Pauw's and Transistors the junctions between the diffusions and the substrate/wells are normally never forward biased. As a result the test engineer needs to evaluate the applied test voltages and connections to the substrate/wells and connections to the diffusions to ensure proper bias conditions.

For example: a P+ Van der Pauw in an N-type Well requires that the Well connection always have the highest positive voltage that is applied. If a separate (5<sup>th</sup> pad) connection is available (not often because there are only 4 SMU's) that can be set to a high voltage. Otherwise the substrate is normally connected to one of the four pads of the Van der Pauw. This pad can be swept with positive voltage thus keeping the substrate/well junction reverse biased.

### GENERAL TEST INSTRUCTIONS

## Each test requires you to:

- 1. Find the structure you want to test

- 2. Place the probes

- 3. Open the test by restoring the "testname"-1 (example PFAM-1) in ICS, view the test setup to see what SMU's do what.

- 4. Set the switch matrix for the HP4145 SMU's to the probes you are using, consistent with the test setup.

- 5. Edit the graph by making changes in the title, moving the cursors to the correct location

- 6. Copy the plot using ctrl print screen, (paste into word, copy from word to power point, crop and paste in correct location)

- 7. Extract the data, such as threshold voltage or LAMBDA and enter the value in the data table in the powerpoint

- 8. Save the powerpoint, minimize the data plot on ICS

- 9. When done email the powerpoint to <a href="mailto:Lynn.Fuller@rit.edu">Lynn.Fuller@rit.edu</a>

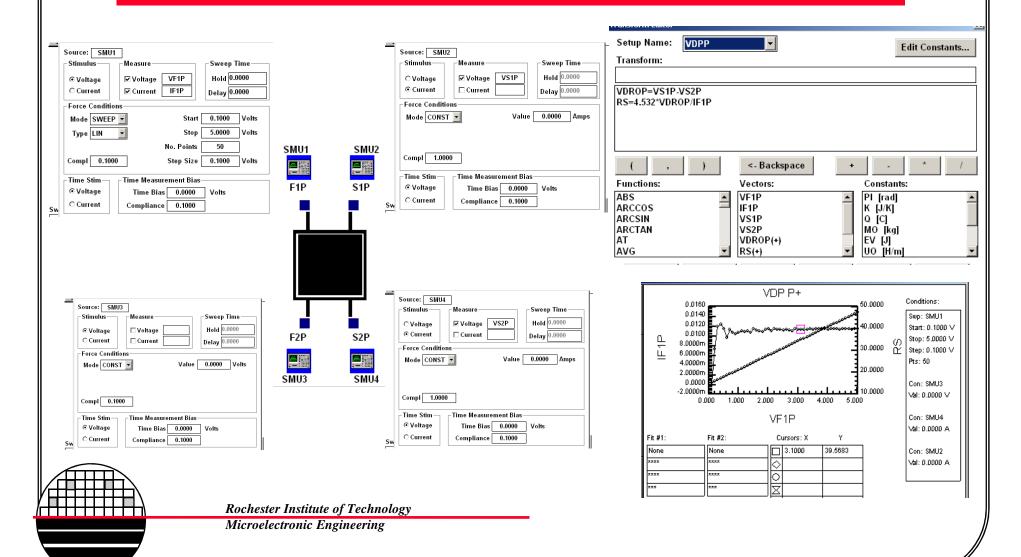

#### TE01 VAN DER PAUW AND CBKR

```

MESA

5/04/06

IGMSINO

S36801

Instruction Group Inquiry

8:31:04

OPADEVOOOW

RIT

Type information. Then Enter.

1=Display document, 5=Display detail

Plant . . . . . . :

RIT

Instruction group . . SUB-CMOS-TEO1 TEST COMPLETED WAFERS

Revision . . . . . . . 150

Opt Subgroup

Text

1.0 Test Resistive Devices

2.0 Test Van Der Paw for Poly, Metal, n+/p+ Diffusion, Well

3.0 Cross Bridge Kelvin Structures for contact resistance

4.0 Via chain yes/no test (enter yes if via chain is good)

5.0 See SPC chart for PolySi Resistance (PolySRes.pps)

6.0 See SPC chart for NRRHOS (NTRHOS.pps)

7.0 See SPC chart for WellRes (WellRes.pps)

8.0 See SPC chart for PTRHOS (PTRHOS.pps)

9.0 Record Rhos(poly, metal, p+, n+, well)

Gc(metal-to-poly)mhos-sq um, Gc(metal-to-p+)mhos-sq um

Bottom

F3=Exit

F4=Prompt

F5=Refresh

F10=View 2

F12=Cancel

```

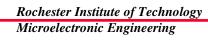

## VAN DER PAUW STRUCTURES FOR SHEET RESISTANCE

Page 25

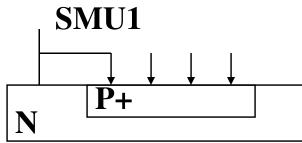

## VAN DER PAUW WITH SUBSTRATE CONNECTIONS

Note: connection to N has to be to the highest voltage used to prevent P+/N junction from being forward biased

### VAN DER PAUW WITH SUBSTRATE CONNECTIONS

### HP 4145 OUTPUT PLOT

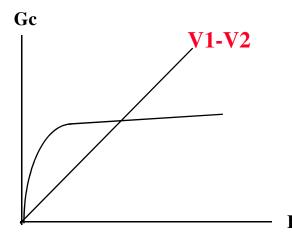

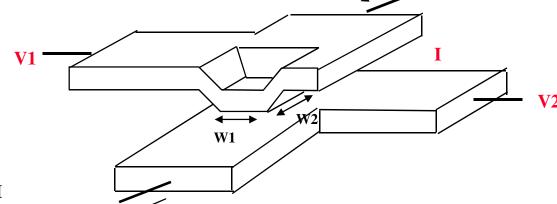

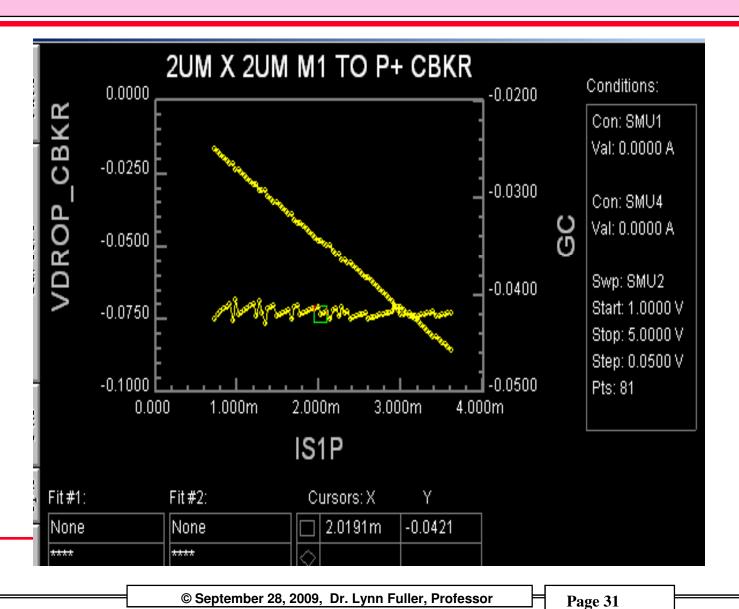

### CROSS BRIDGE KELVIN RESISTANCE TEST STRUCTURES FOR CONTACT RESISTANCES

$$Rc = \frac{(V1-V2)}{I} \quad ohms$$

$$Gc = \frac{I}{(V1-V2)} \frac{1}{W1 \times W2} \quad mhos/\mu m^2$$

Rochester Institute of Technology

Microelectronic Engineering

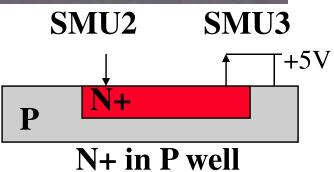

### CBKR WITH SUBSTRATE CONNECTIONS

N+ in P well

P+ in N well

Poly

Note: connection to N+ has to be to the highest voltage used to prevent N+/P junction from being forward biased. SMU2 is swept from 0 to +5V, SMU3 is fixed at +5V

see next page.

### HP 4145 OUTPUT PLOT

#### TE02 TRANSISTORS

```

5/04/06

MESA

IGMSINO

S36801

8:35:54

Instruction Group Inquiry

QPADEVOOOW

RIT

Type information. Then Enter.

1=Display document, 5=Display detail

RIT

Plant . . . . . . :

Instruction group . . SUB-CMOS-TE02

TEST COMPLETED WAFERS

Revision . . . . . . 150

Opt Subgroup Text

1.0 Test PMOS and NMOS Transistors

for threshold voltage, tranconductance, lambda,

subthreshold slope, min and max current value on the

subthreshold test

2.0 Record VTn, VTp, gmn, gmp, sub-Vt-slope, Isub-min, Isub-max,

Lambda, transistor width&length for nmos & pmos, Vt field

```

F10=View 2 F12=Cancel

F5=Refresh

F3=Exit

F4=Prompt

**Bottom**

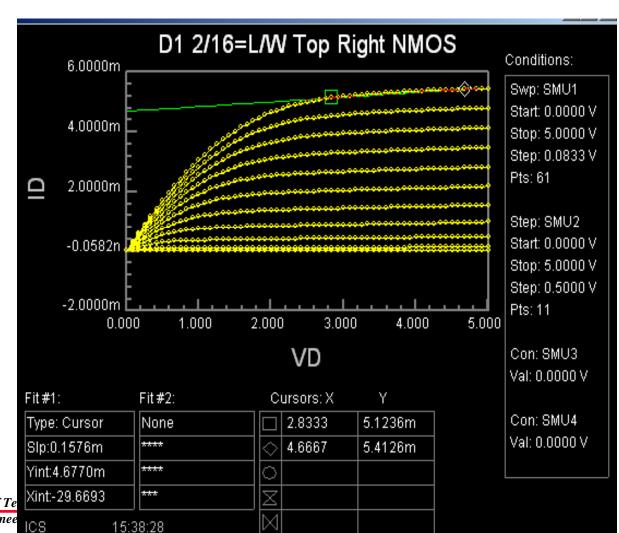

## TRANSISTOR FAMILY OF CURVES, ID-VDS

## Lambda = slope/Idsat

Rochester Institute of Te Microelectronic Enginee

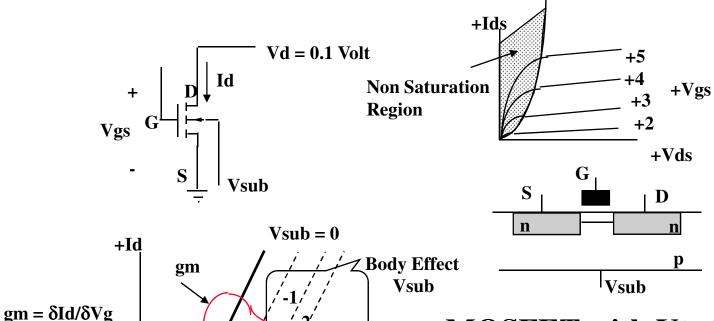

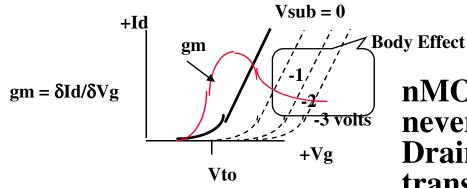

## TRANSISTOR LINEAR REGION VT, GM

+Vg

Rochester Institute of Technology Microelectronic Engineering

Vto

nMOSFET with Vt=1, since the Drain is at 0.1 volts and the source is at zero. Both drain and source will be on at gate voltages greater than 1.1 volt. the transistor will be in the non saturation region.

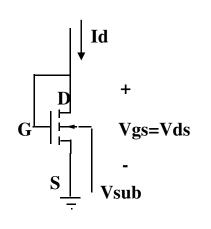

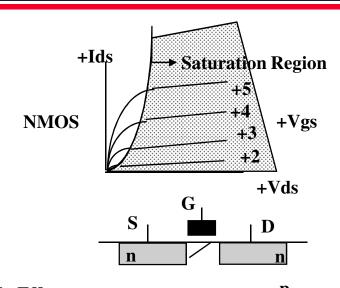

## TRANSISTOR SATURATION REGION VT, GM

nMOSFET with Vt=1, Drain end is never on because Voltage Gate to Drain is Zero. Therefore this transistor is always in Saturation Region if the gate voltage is above the threshold voltage.

| |Vsub

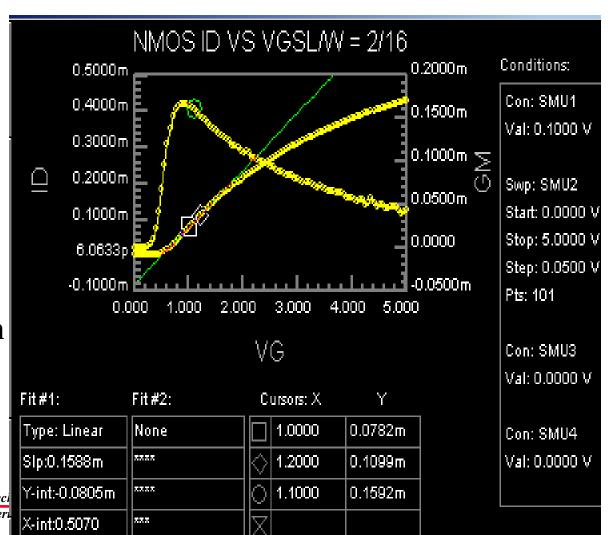

### NMOS ID-VGS TEST

Same test for field oxide threshold voltage

gm = 0.16 mmho/16μm = 0.010 S/mm

Vt = 0.507 volts

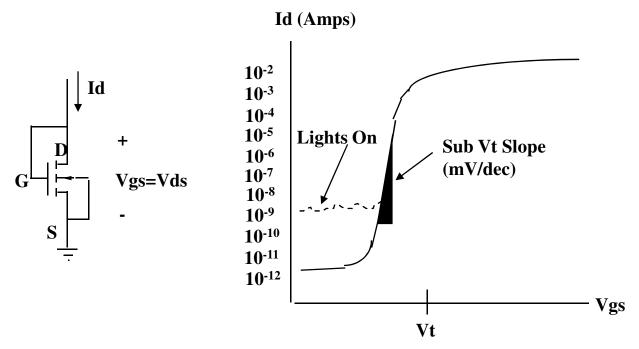

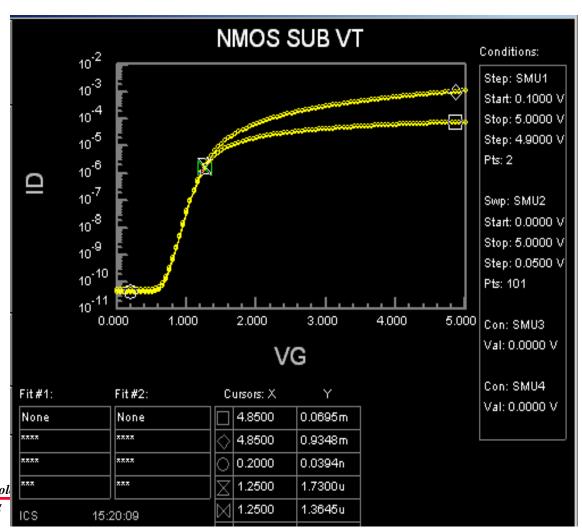

#### TRANSISTOR SUB THRESHOLD ID-VGS

The subthreshold characteristics are important in VLSI circuits because when the transistors are off they should not carry much current since there are so many transistors. (typical value about 100 mV/decade)

Rochester Institute of Technology

Microelectronic Engineering

#### SUB THRESHOLD CHARACTERISTICS

$Ion/Ioff = \sim 6 Decades$

Swing =  $\sim 100 \text{ mV/dec}$

DIBL@1nA/ $\mu$ m =  $\Delta$ Vg/ $\Delta$ Vd = 0 mV/V

Rochester Institute of Technol Microelectronic Engineering

#### TE03 INTEGRATED CIRCUITS

```

MESA

5/04/06

IGMSINQ

S36801

8:37:20

Instruction Group Inquiry

OPADEVOOOW

RIT

Type information. Then Enter.

1=Display document, 5=Display detail

Plant . . . . . . :

RIT

Instruction group . .

SUB-CMOS-TE03

TEST COMPLETED WAFERS

Revision . . . . . .

150

Opt Subgroup Text

1.0 Test Inverters and Ring Oscillator

2.0 Record ViL, ViH, VoL, VoH, Vinv, Imax, Ring Oscillator

Frequency, Number of Stages

```

**Bottom**

F3=Exit F4=Prompt F5=Refresh F10=View 2 F12=Cancel

Rochester Institute of Technology Microelectronic Engineering

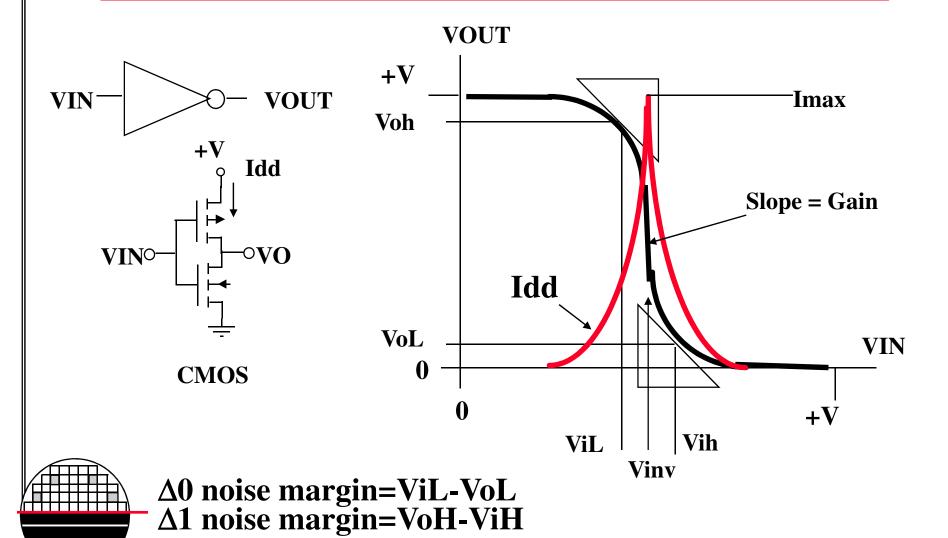

## **INVERTERS**

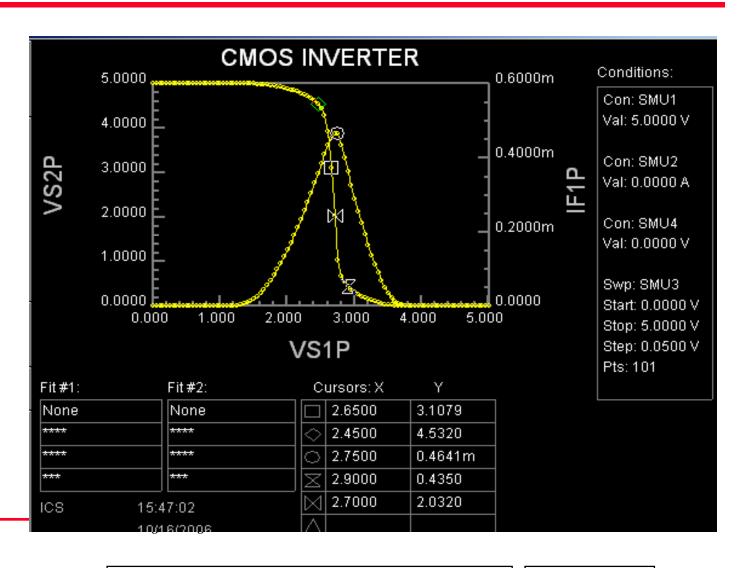

#### CMOS INVERTER VOUT VS VIN

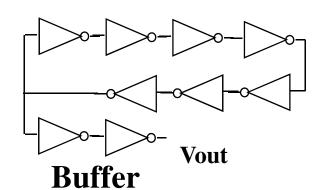

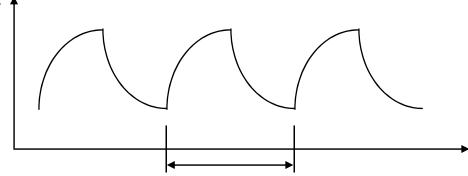

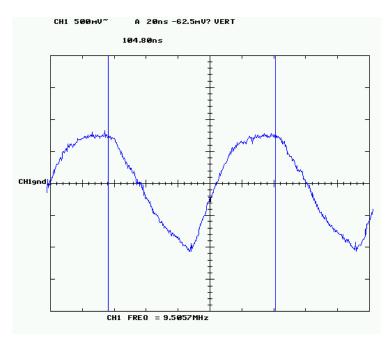

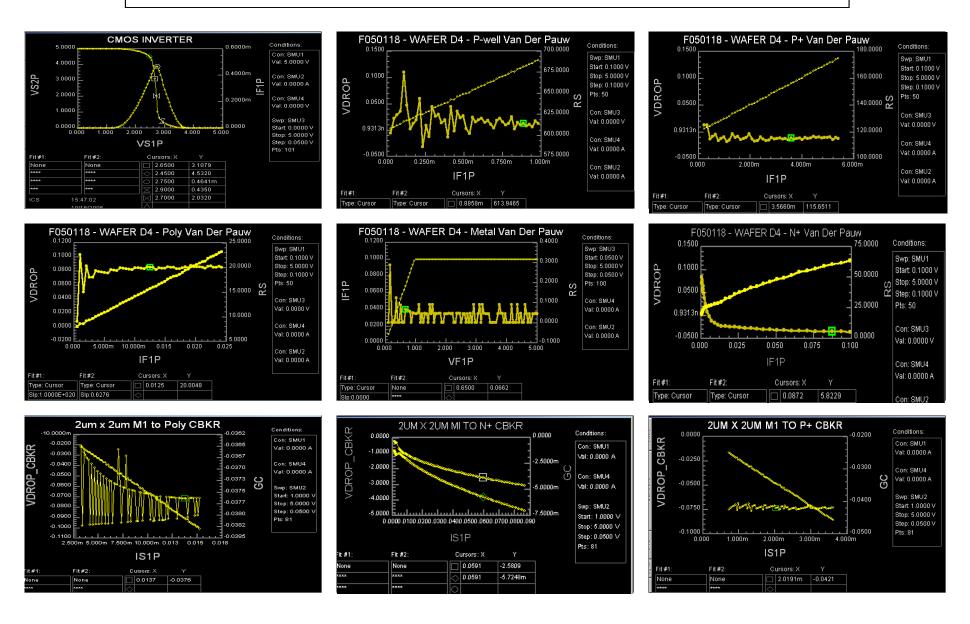

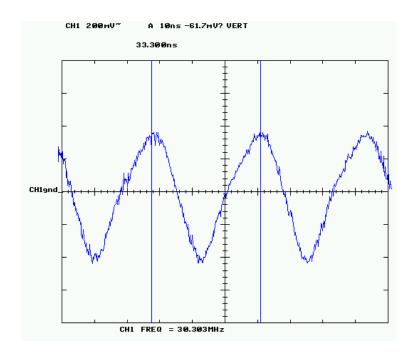

# RING OSCILLATOR, td

Seven stage ring oscillator with two output buffers

$$td = T/2N$$

td = gate delay

N = number of stages

T = period of oscillation

Vout 4

T = period of oscillation

## RING OSCILLATOR MEASUREMENTS

73 Stage Ring at 5V, td = 0.712ns

Rochester Institute of Technology

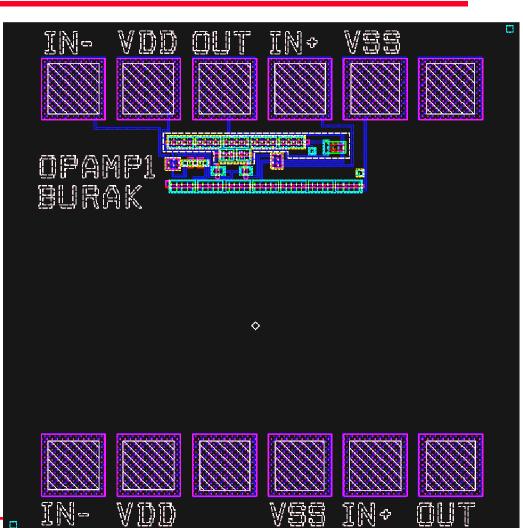

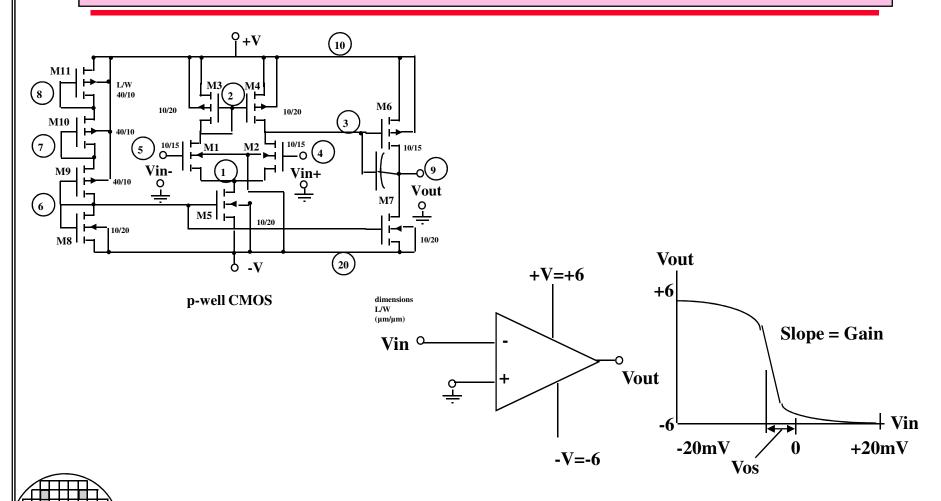

## **OPERATIONAL AMPLIFIER**

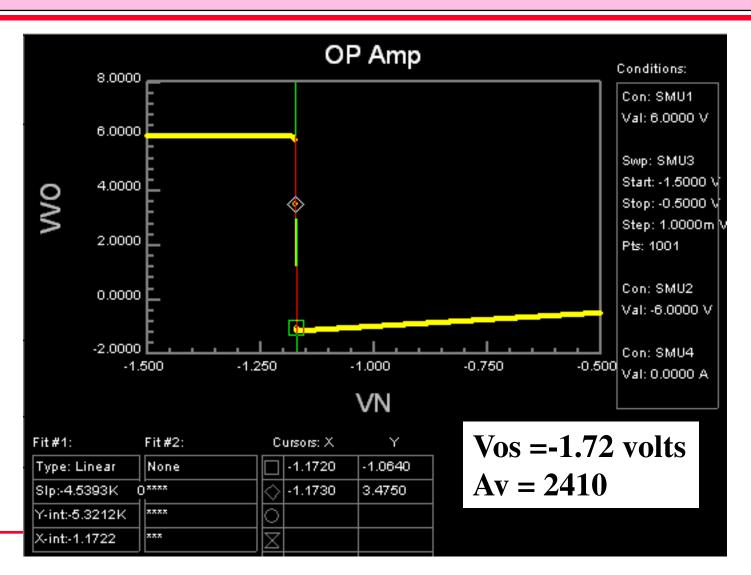

Rochester Institute of Technology Microelectronic Engineering Set up the HP 4145 to sweep the Vin from -20 mV to +20 mV in 0.001V steps. Measure Gain and Input offset voltage.

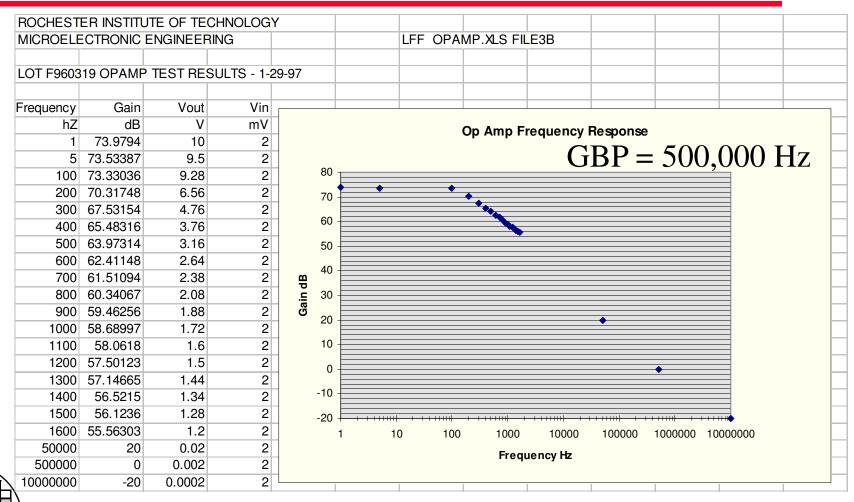

#### AC TEST RESULTS

Rochester Institute of Technology Microelectronic Engineering

#### **OPERATIONAL AMPLIFIER**

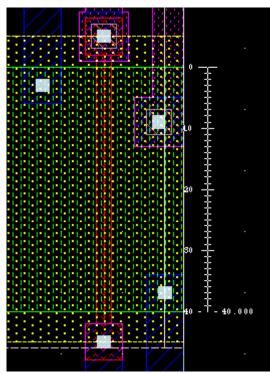

#### **TE04**

```

3/09/08

MESA

IGMSINO

S36801

Instruction Group Inquiry

12:59:49

OPADEV001H

RIT

Type information. Then Enter.

1=Display document, 5=Display detail

Plant . . . . . . :

RIT

Instruction group . .

TE04

WAFER MAP OF VT

Revision . . . . . .

Opt Subgroup Text

1.0 Take data for wafer map of Vt, test all transistors

(see wafermap.pps)

2.0 Compute +/- 10%, 20%, 30%, 40% of target:

CMOS Targets are +/-1.0

Record data row by row, each character in a row

represents a different column (die), the value will be

5 if within 10% of target

4 if between -30% and -10% of target

6 if between +10% and +30% of target

3 if between -50% and -30% of target, etc.

Bottor

F10=View 2 F12=Cancel

F5=Refresh

F3=Exit

F4=Prompt

```

© September 28, 2009, Dr. Lynn Fuller, Professor

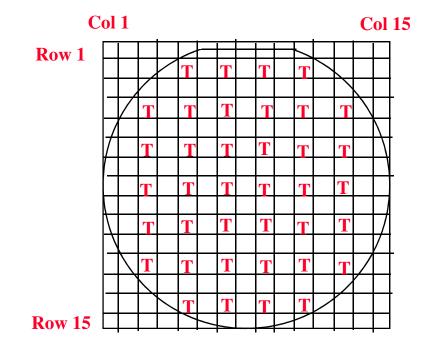

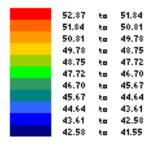

## WAFER MAPS FOR MESA

nmos Vt target +1 000000000000000000

row 1 is the first row in which a full die is located column 1 is the first column in which a full die is located

Rochester Institute of Technology

#### WAFER MAPS FOR MESA

## Code

```

no die

value<(Target-70%)</li>

(Target-70%)

(Target-50%)

(Target-50%)

(Target-30%)

(Target-10%)

(Target-10%)

(Target+10%)

(Target+30%)

(Target+30%)

(Target+50%)

(Target+70%)

(Target+70%)

```

Rochester Institute of Technology

#### WAFER MAP

Example: Given a wafer with test chips located as shown and nmos threshold voltage data encoded and stored in MESA as shown. Reconstruct a wafer map using EXCELL spreadsheet.

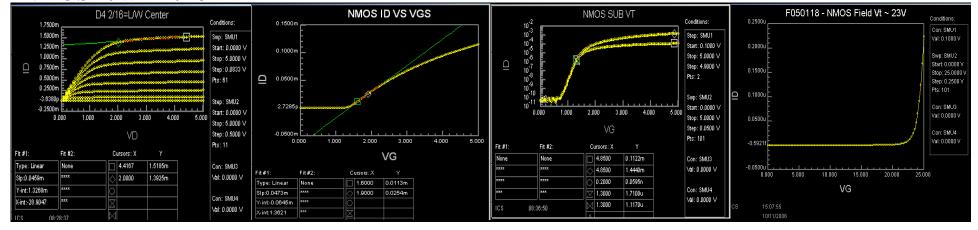

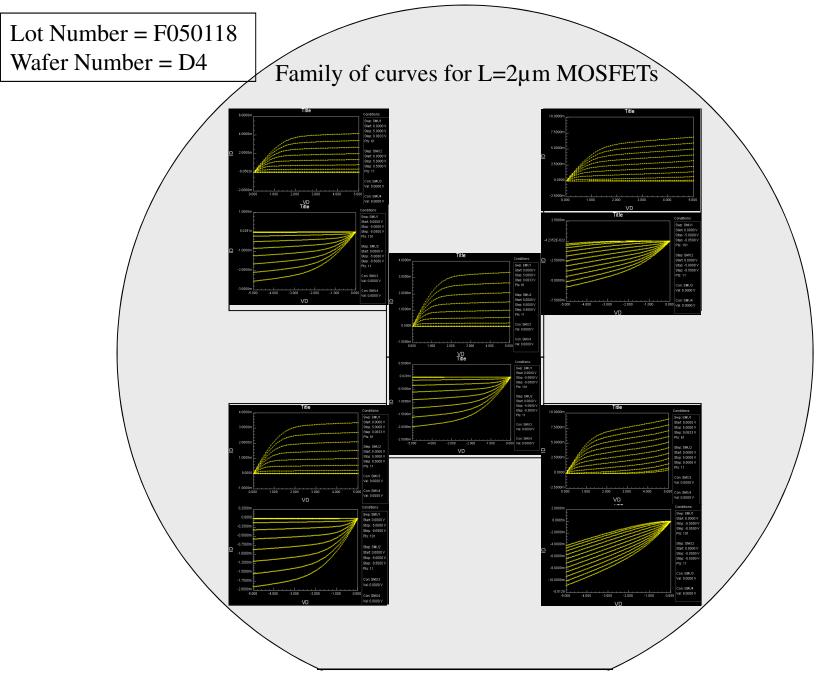

#### MOSFET IV CHARACTERISTICS

Lot Number = F050118

Wafer Number = D4

Date = 11-17-2006

Process = SMFL CMOS

Product = DAC03

#### NMOS L/W = 2/16

NFAM NVT NSUB NFIELD

#### PMOS L/W = 2/16

## MOSFET EXTRACTED PARAMETERS

Lot Number = F050118 – Wafer Number = D4, Die Location R= , C=

|                                                     | PMOS    | NMOS    | Units   |

|-----------------------------------------------------|---------|---------|---------|

| Mask Length / Width                                 | 2/16    | 2/16    | μm      |

| VT                                                  | -1.51   | 1.36    | V       |

| Lambda (for Vgs = Vdd)                              | 0.115   | 0.0417  | V-1     |

| Max gm / mm of channel width                        | 21.3    | 31.3    | S/mm    |

| Idrive                                              | 54.4    | 93.8    | μA/μm   |

| Ion/Ioff @ Vd = 0.1V                                | 6       | 5       | Decades |

| Ion/Ioff @ Vd = 5V                                  | 7       | 6       | Decades |

| Ioff @ Vd = 0.1V                                    | 5.9e-11 | 5.0e-10 | A/μm    |

| Ioff @ Vd = 5V                                      | 5.9e-11 | 5.0e-10 | A/μm    |

| Sub-Vt Slope @ Vd = 0.1V                            | 90      | 190     | mV/Dec  |

| Sub-Vt Slope @ Vd = 5 V                             | 90      | 190     | mV/Dec  |

| <b>DIBL</b> @1nA/ $\mu$ m = $\Delta V_g/\Delta V_d$ | 0       | 0       | mV/V    |

| Field VT                                            | -23     | 23      | V       |

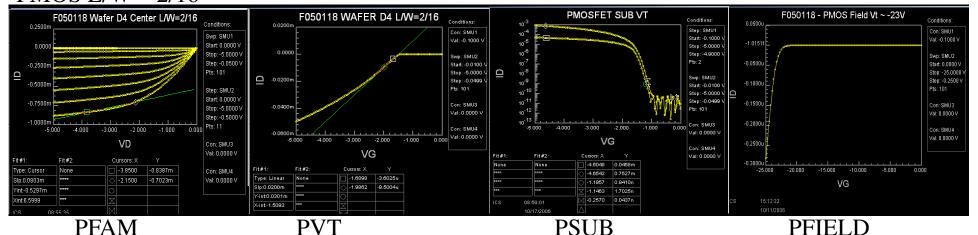

## INVERTERS, VAN DER PAUW AND CBKR

Lot Number = F050118 – Wafer Number = D4, Die Location R=, C=

# EXTRACTED PARAMETERS FROM INVERTERS, VAN DER PAUW AND CBKR

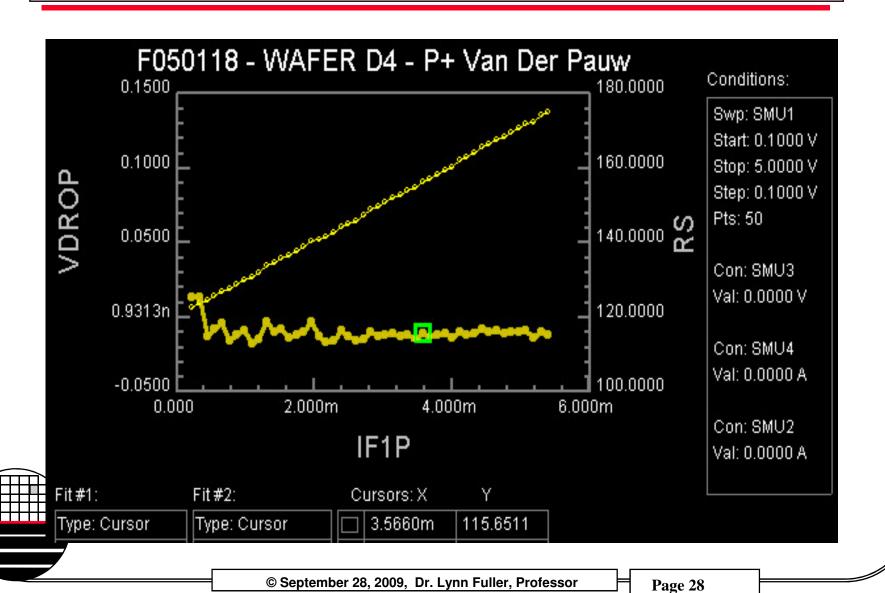

Lot Number = F050118 – Wafer Number = D4, Die Location R=, C=

| <b>Contact Gs</b> | CBKR |          |

|-------------------|------|----------|

| P+                | 42   | mmho/µm² |

| N+                | 8    | mmho/μm² |

| poly              | 37   | mmho/μm² |

|          | Ring Oscillator | Vdd=5<br>V |

|----------|-----------------|------------|

| # Stages | 73              |            |

| Period   | 104             | nsec       |

| td       | 0.712           | nsec       |

| Rhos     | Van der Pauw    |            |

| P+       | 115             | Ohms       |

| N+       | 5.8             | Ohms       |

| well     | 614             | Ohms       |

| Poly     | 20.0            | Ohms       |

| Al       | 0.0662          | Ohms       |

|            | Inverter |    |

|------------|----------|----|

| VinL       | 2.4      | V  |

| VinH       | 3        | V  |

| VoL        | 0.4      | V  |

| VoH        | 4.5      | V  |

| Vinv       | 2.6      | V  |

| Imax       | 4.5      | mA |

| Gain       | -21.5    |    |

| Δ0=ViL-VoL | 2.0      | V  |

| Δ1=VoH-ViH | 1.5      | V  |

|        | OpAmp |        |

|--------|-------|--------|

| Gain   | None  |        |

| Offset | None  | mVolts |

| GBW    | None  | Hz     |

|       | VIA CHAIN |      |

|-------|-----------|------|

| M1-P+ | None      | ohms |

| M1-M2 | None      | ohms |

73 Stage Ring at 5V, td = 0.712ns

73 Stage Ring at 6V, td = 0.228ns

$2\mu m/32\mu m$  L/W NMOS AND PMOS

#### **RESULTS**

## A test specification has been developed

Sheet Resistance of Poly, Metal, P+ DS, N+ DS, Well

Transistor Vt, gm, sub threshold slope, Lambda, field

Vt

ICs, inverter, ring oscillator, opamp

A history/data base has been built

Analog parametric tests for some devices has been developed (much more to do)

## **FUTURE WORK**

More Automation

Improved Wafer Mapping

More Complete Testing

Improved Analog Testing

Improved Digital Testing

## **CONCLUSION**

Testing is very time consuming. It takes us 9 hours to do all the specified tests and even then we only test a few devices on a wafer.

Currently we test about 1% of the devices

#### **HOMEWORK - CMOS TEST**

- 1. How is Lambda, Vt and gm found from the transistor family of curves? Show example calculations.

- 2. How are Vt and gm found from the Id-Vgs plot?

- 3. Explain how sub threshold swing, Ion/Ioff, and DIBL are found. Show example calculations and correct units of measure.

- 4. What is the significance of inverter noise margin.

- 5. What is the purpose of the ring oscillator test structure.